Bill Hargin

Z-zero

叠 层 设 计

设计中的设计

印制电路设计师指南

印制电路设计师指南

叠层设计

设计中的设计

Bill Hargin

Z-zero

© 2022 IPC Publishing Group, Inc.

All rights reserved.

IPC Publishing Group, Inc.

dba I-Connect007

3000 Lakeside Drive, Suite 105N

Bannockburn, IL 60015 USA

ISBN :979-8-9856020-9-8

更多中文书籍请访问我们的图书馆查看

同行评审 作者介绍

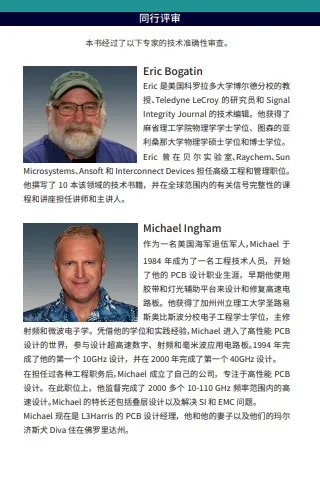

Eric Bogatin

Eric 是美国科罗拉多大学博尔德分校的教

授、Teledyne LeCroy 的研究员和 Signal

Integrity Journal 的技术编辑。他获得了

麻省理工学院物理学学士学位、图森的亚

利桑那大学物理学硕士学位和博士学位。

Eric 曾 在 贝 尔 实 验 室、Raychem、Sun

Microsystems、Ansoft 和 Interconnect Devices 担任高级工程和管理职位。

他撰写了 10 本该领域的技术书籍,并在全球范围内的有关信号完整性的课

程和讲座担任讲师和主讲人。

Michael Ingham

作为一名美国海军退伍军人,Michael 于

1984 年成为了一名工程技术人员,开始

了他的 PCB 设计职业生涯,早期他使用

胶带和灯光辅助平台来设计和修复高速电

路板。他获得了加州州立理工大学圣路易

斯奥比斯波分校电子工程学士学位,主修

射频和微波电子学。凭借他的学位和实践经验,Michael 进入了高性能 PCB

设计的世界,参与设计超高速数字、射频和毫米波应用电路板。1994 年完

成了他的第一个 10GHz 设计,并在 2000 年完成了第一个 40GHz 设计。

在担任过各种工程职务后,Michael 成立了自己的公司,专注于高性能 PCB

设计。在此职位上,他监督完成了 2000 多个 10-110 GHz 频率范围内的高

速设计。Michael 的特长还包括叠层设计以及解决 SI 和 EMC 问题。

Michael 现在是 L3Harris 的 PCB 设计经理,他和他的妻子以及他们的玛尔

济斯犬 Diva 住在佛罗里达州。

本书经过了以下专家的技术准确性审查。

作者介绍

Bill Hargin

Bill Hargin 是 Z-zero 的 创 始 人,

PCB 叠 层 设 计 和 材 料 选 择 软 件

Z-planner Enterprise 的 开 发 者。

Hargin 是行业先驱,在 PCB 信号

完整性和制造领域拥有超过 25 年

的工作经验。Hargin 是《印制电路

设计与制造》杂志的专栏作家,撰

写了数十篇关于信号完整性、叠层设计和材料选择的文章,同时他还是

《印刷电路手册》的特约作者。

Bill 是 PCB West 和 DesignCon 演讲者和评审组的常客,来自 30 多个

国家和地区的 10000 多名工程师和 PCB 设计师参加了他关于叠层规划、

信号完整性和高速 PCB 设计方面的研讨会。在创立 Z-zero 之前,他在

Mentor Graphics 工作了八年多,专注于高速信号完整性和 PCB 仿真

软件,并担任 HyperLynx SI 软件的营销总监。随后,他担任中国台湾

南亚的 PCB 材料部门的北美营销总监。他获得了华盛顿州立大学机械

工程学位和 MBA 学位。

Bill 目前住在华盛顿州,是一名小联盟棒球和垒球的热心志愿者。

机械世界与电气世界

材料的重要性

了解材料规格书

降低损耗

材料鉴定与选择

阻抗规划

玻纤编织效应

刚柔结合材料

总结

参考文献

关于 Z-zero 和西门子数字化工业软件

目录

1

7

15

23

31

37

43

51

59

65

67

前言

第一章

第二章

第三章

第四章

第五章

第六章

第七章

第八章

1

机械世界与

电气世界

又是一本关于叠层的书?

如果您想问这个问题,我想知道您所想到的书,因为几年前我一

直在找关于这个主题的书籍。我有很多 PCB 信号完整性(SI) 方面的

书籍,但到目前为止我只在其中找到了一章关于叠层设计的内容。

每当我与 SI 顾问(以 SI 咨询为生的人)交谈时,我都会问他们

“你被紧急叫去救火的存在严重 SI 问题的项目中,有多少存在叠层

问题? ”

到目前为止,我得到的所有答案都是“100%”。

一个高速 PCB 能够被制造出来,和一个设计应该是这样的构造

之间的区别在于设计本身的支柱——叠层。叠层关乎每一个高速信号,

但关于它的文章却出人意料地少。

我的工作中遇到过很多 PCB 叠层,根据不同的设计人员和所使

用的工具,叠层不尽相同,多数情况下,设计团队都可以通过改进其

中的制造参数来优化阻抗和信号损耗。随着信号速度越来越高,现在

的信号完整性关键因素不仅包括阻抗,还包括损耗、铜箔粗糙度和

玻纤编织效应。其实,在 PCB 物理制造的过程中所发生的一切事情

都会对信号质量产生负面影响,因此不仅需要考虑 PCB 叠层的细节,

还需要考虑设计中每个 PCB 制造商的叠层差异。

我比较不理解的是很少有书籍或文章解释清楚了叠层在哪些方

面会影响信号。这不会是关于这个主题的最后一本书,我希望能抛砖

引玉,引发更多对叠层规划和材料选择的讨论,从而让大家都深刻理

解我所说的“设计中的设计”。

前言

2

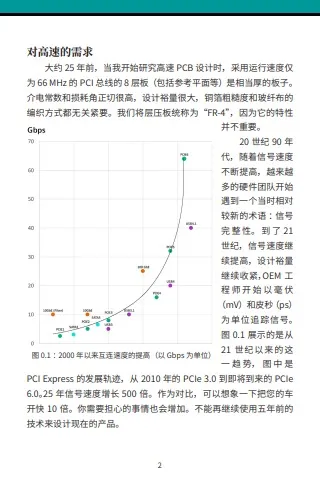

对高速的需求

大约 25 年前,当我开始研究高速 PCB 设计时,采用运行速度仅

为 66 MHz 的 PCI 总线的 8 层板(包括参考平面等)是相当厚的板子。

介电常数和损耗角正切很高,设计裕量很大,铜箔粗糙度和玻纤布的

编织方式都无关紧要。我们将层压板统称为“FR-4”,因为它的特性

并不重要。

20 世纪 90 年

代,随着信号速度

不断提高,越来越

多的硬件团队开始

遇到一个当时相对

较新的术语 :信号

完 整 性。 到 了 21

世纪,信号速度继

续提高,设计裕量

继续收紧,OEM 工

程 师 开 始 以 毫 伏

(mV) 和皮秒 (ps)

为单位追踪信号。

图 0.1 展示的是从

21 世 纪 以 来 的 这

一 趋 势, 图 中 是

PCI Express 的发展轨迹,从 2010 年的 PCIe 3.0 到即将到来的 PCIe

6.0。25 年信号速度增长 500 倍。作为对比,可以想象一下把您的车

开快 10 倍。你需要担心的事情也会增加。不能再继续使用五年前的

技术来设计现在的产品。

图 0.1 :2000 年以来互连速度的提高(以 Gbps 为单位)

3

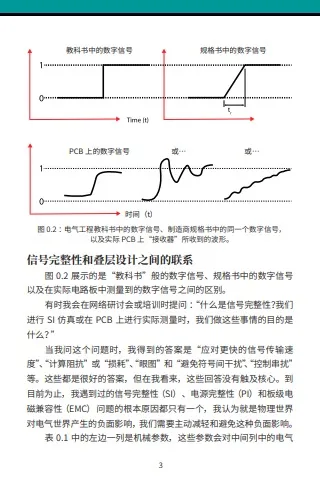

信号完整性和叠层设计之间的联系

图 0.2 展示的是“教科书”般的数字信号、规格书中的数字信号

以及在实际电路板中测量到的数字信号之间的区别。

有时我会在网络研讨会或培训时提问 :“什么是信号完整性?我们

进行 SI 仿真或在 PCB 上进行实际测量时,我们做这些事情的目的是

什么? ”

当我问这个问题时,我得到的答案是“应对更快的信号传输速

度” 、“计算阻抗”或“损耗” 、“眼图”和“避免符号间干扰”、“控制串扰”

等。这些都是很好的答案,但在我看来,这些回答没有触及核心。到

目前为止,我遇到过的信号完整性 (SI) 、电源完整性 (PI) 和板级电

磁兼容性 (EMC) 问题的根本原因都只有一个,我认为就是物理世界

对电气世界产生的负面影响,我们需要主动减轻和避免这种负面影响。

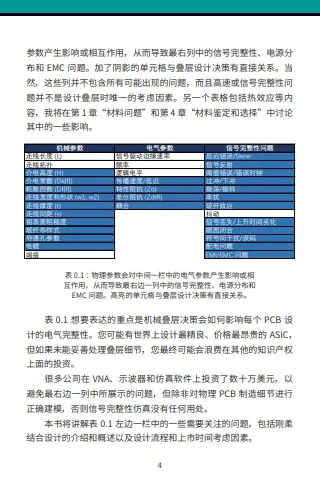

表 0.1 中的左边一列是机械参数,这些参数会对中间列中的电气

图 0.2 :电气工程教科书中的数字信号、制造商规格书中的同一个数字信号,

以及实际 PCB 上“接收器”所收到的波形。

教科书中的数字信号 规格书中的数字信号

PCB 上的数字信号 或… 或…

时间(t)

4

参数产生影响或相互作用,从而导致最右列中的信号完整性、电源分

布和 EMC 问题。加了阴影的单元格与叠层设计决策有直接关系。当

然,这些列并不包含所有可能出现的问题,而且高速或信号完整性问

题并不是设计叠层时唯一的考虑因素。另一个表格包括热效应等内

容,我将在第 1 章“材料问题”和第 4 章“材料鉴定和选择”中讨论

其中的一些影响。

表 0.1 想要表达的重点是机械叠层决策会如何影响每个 PCB 设

计的电气完整性。您可能有世界上设计最精良、价格最昂贵的 ASIC,

但如果未能妥善处理叠层细节,您最终可能会浪费在其他的知识产权

上面的投资。

很多公司在 VNA、示波器和仿真软件上投资了数十万美元,以

避免最右边一列中所展示的问题,但除非对物理 PCB 制造细节进行

正确建模,否则信号完整性仿真没有任何用处。

本书将讲解表 0.1 左边一栏中的一些需要关注的问题,包括刚柔

结合设计的介绍和概述以及设计流程和上市时间考虑因素。

机械参数 电气参数 信号完整性问题

走线长度 (L) 信号驱动边缘速率 延迟错误/Skew

走线拓扑 频率 信号反射

介电高度 (H) 逻辑电平 阈值错误/错误时钟

介电常数 (Dk[f]) 传播速度/延迟 过冲/下冲

耗散因数 (Df[f]) 特性阻抗 (Zo) 振荡/振铃

走线宽度和形状 (w1, w2) 差分阻抗 (Zdiff) 串扰

走线厚度 (t) 耦合 玻纤效应

走线间距 (s) 抖动

铜表面粗糙度 信号丢失/上升时间劣化

玻纤布样式 眼图闭合

导通孔参数 符号间干扰/误码

电镀 配电问题

端接 EMI/EMC 问题

表 0.1 :物理参数会对中间一栏中的电气参数产生影响或相

互作用,从而导致最右边一列中的信号完整性、电源分布和

EMC 问题。高亮的单元格与叠层设计决策有直接关系。

5

“印制电路板制造中

的所有制程都会影响

信号质量。这就是我

们在信号完整性上花

费如此多时间的原

因——电气世界和物

理世界在不断冲突。”

–Bill Hargin

7

25 年前,在出现信号完整性软件的早期,信号完整性成为主流

设计实践之前,我就对所有人说,信号完整性分析应该在 PCB 布线

之前进行。在当时,这是新的方法,与当时的做法完全不同。现在所

有人都在这样做。

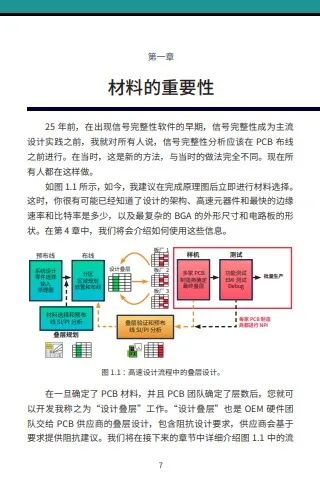

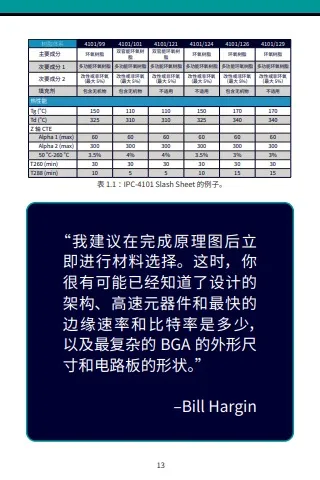

如图 1.1 所示,如今,我建议在完成原理图后立即进行材料选择。

这时,你很有可能已经知道了设计的架构、高速元器件和最快的边缘

速率和比特率是多少,以及最复杂的 BGA 的外形尺寸和电路板的形

状。在第 4 章中,我们将会介绍如何使用这些信息。

在一旦确定了 PCB 材料,并且 PCB 团队确定了层数后,您就可

以开发我称之为“设计叠层”工作。“设计叠层”也是 OEM 硬件团

队交给 PCB 供应商的叠层设计,包含阻抗设计要求,供应商会基于

要求提供阻抗建议。我们将在接下来的章节中详细介绍图 1.1 中的流

第一章

材料的重要性

图 1.1 :高速设计流程中的叠层设计。

系统设计 设计叠层

零件选择

输入

原理图

预布线

分区

区域规划

放置和布线

布线

板厂 1

板厂 2

板厂 3

多家 PCB

制造商确定

最终叠层

样机 测试

功能测试

EMI 测试

Debug

批量生产

每家 PCB 制造 叠层验证和预布 商都进行 NPI

线 SI/PI 分析

材料选择和预布

线 SI/PI 分析

叠层规划

系统设计 设计叠层

零件选择

输入

原理图

预布线

分区

区域规划

放置和布线

布线

板厂 1

板厂 2

板厂 3

多家 PCB

制造商确定

最终叠层

样机 测试

功能测试

EMI 测试

Debug

批量生产

每家 PCB 制造 叠层验证和预布 商都进行 NPI

线 SI/PI 分析

材料选择和预布

线 SI/PI 分析

叠层规划

每次更改约 $100 每次更改约 $1,000 每次更改约 $10,000 - $100,000

这里关注叠层设计变更 消除这里成本更高的设计更改

8

程。在第 1 章中,我想从宏观的视角、从 40000 英尺的高度来介绍

PCB 叠层设计的组成部分。

以绿色显示的叠层是设计叠层,需要与以红色显示的 PCB 制造

商叠层进行来回交换。这样的交换意味着 OEM 硬件团队在积极开发

设计叠层,并将其发送给制造商,然后让每个 PCB 制造商返回他们

自己的叠层设计建议。每个生产阶段(样机、小批量和批量)可能会

有不同的制造商。这时,您需要对您与制造商商定的最终叠层进行布

线后信号完整性验证。

这里的要点是您可以在整个设计过程的前端选择使用哪些材料。

如果你这样做了,叠层设计过程的其余部分会很自然地完成。

在第 5 章中,我会讲解阻抗规划,由于制程是基于真实材料的,

所以阻抗规划非常有价值。

在第 2 章开始讲解 PCB 材料规格书参数之前,我们有必要先来

探讨 PCB 叠层的组成部分。

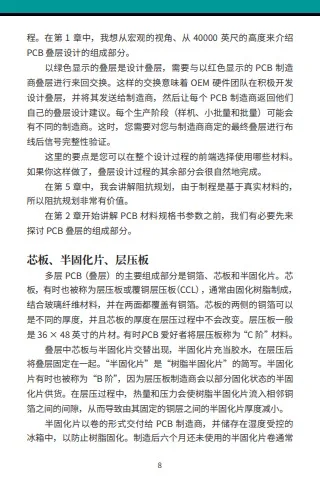

芯板、半固化片、层压板

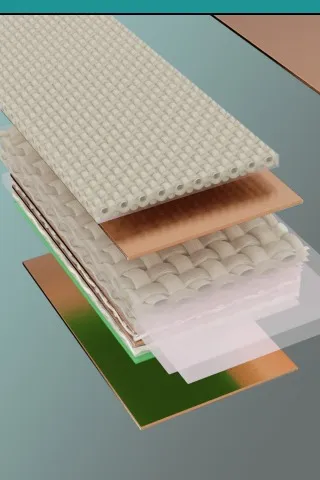

多层 PCB (叠层)的主要组成部分是铜箔、芯板和半固化片。芯

板,有时也被称为层压板或覆铜层压板 (CCL) ,通常由固化树脂制成,

结合玻璃纤维材料,并在两面都覆盖有铜箔。芯板的两侧的铜箔可以

是不同的厚度,并且芯板的厚度在层压过程中不会改变。层压板一般

是 36 × 48 英寸的片材。有时,PCB 爱好者将层压板称为“C 阶”材料。

叠层中芯板与半固化片交替出现,半固化片充当胶水,在层压后

将叠层固定在一起。“半固化片”是“树脂半固化片”的简写。半固化

片有时也被称为“B 阶”,因为层压板制造商会以部分固化状态的半固

化片供货。在层压过程中,热量和压力会使树脂半固化片流入相邻铜

箔之间的间隙,从而导致由其固定的铜层之间的半固化片厚度减小。

半固化片以卷的形式交付给 PCB 制造商,并储存在湿度受控的

冰箱中,以防止树脂固化。制造后六个月还未使用的半固化片卷通常

9

会被报废,因为 6 个月后,树脂的流动将不再可预测。出于这个原因,

PCB 制造商只会储存他们认为足够在未来三到四个月内使用的半固化

片。由于芯板经过了完全固化,并且铜可以防止介电材料直接暴露在

湿气中,所以芯板的保质期更长。

所使用的芯板和半固化片组合通常来自各自的材料供应商。同一

种材料类型通常会有多种层压板可供选择,但可供选择的半固化片样

式就会少很多。原因是半固化片是单层卷材,而芯板可以是单层、双层,

甚至多达八层的 7628 玻纤布组成。

玻纤布和树脂

PCB 中半固化片和芯板不导电介电层中包含树脂和玻璃纤维两种

材料的组合。树脂提供介电功能的同时还充当粘合剂的角色以粘附到

铜箔上,而玻璃纤维负责增强结构强度,就像混凝土中的钢筋。单独

的树脂很坚硬,但没有弹性。添加玻璃纤维能够加强结构并为树脂提

供了弹性的可供粘附的表面。

图 1.2 :典型的叠层结构,外面的铜箔是由 PCB 制造商

提供的,半固化片和芯板在叠层中交替出现。

第一层

第二、三层

第四、五层

第六层

铜箔

半固化片

芯板

半固化片

芯板

半固化片

铜箔

10

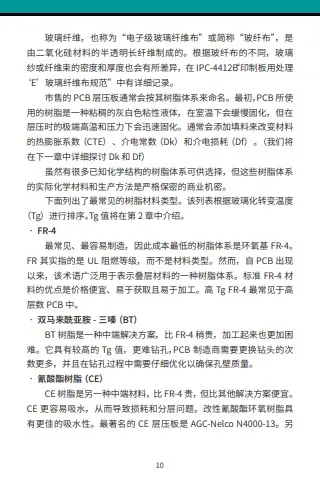

玻璃纤维,也称为“电子级玻璃纤维布”或简称“玻纤布”,是

由二氧化硅材料的半透明长纤维制成的。根据玻纤布的不同,玻璃

纱或纤维束的密度和厚度也会有所差异,在 IPC-4412B“印制板用处理

‘E’玻璃纤维布规范”中有详细记录。

市售的 PCB 层压板通常会按其树脂体系来命名。最初,PCB 所使

用的树脂是一种粘稠的灰白色粘性液体,在室温下会缓慢固化,但在

层压时的极端高温和压力下会迅速固化。通常会添加填料来改变材料

的热膨胀系数 (CTE) 、介电常数 (Dk) 和介电损耗 (Df) 。(我们将

在下一章中详细探讨 Dk 和 Df)

虽然有很多已知化学结构的树脂体系可供选择,但这些树脂体系

的实际化学材料和生产方法是严格保密的商业机密。

下面列出了最常见的树脂材料类型。该列表根据玻璃化转变温度

(Tg) 进行排序。Tg 值将在第 2 章中介绍。

• FR-4

最常见、最容易制造,因此成本最低的树脂体系是环氧基 FR-4。

FR 其实指的是 UL 阻燃等级,而不是材料类型。然而,自 PCB 出现

以来,该术语广泛用于表示叠层材料的一种树脂体系。标准 FR-4 材

料的优点是价格便宜、易于获取且易于加工。高 Tg FR-4 最常见于高

层数 PCB 中。

• 双马来酰亚胺 - 三嗪 (BT)

BT 树脂是一种中端解决方案,比 FR-4 稍贵,加工起来也更加困

难。它具有较高的 Tg 值,更难钻孔,PCB 制造商需要更换钻头的次

数更多,并且在钻孔过程中需要仔细优化以确保孔壁质量。

• 氰酸酯树脂 (CE)

CE 树脂是另一种中端材料,比 FR-4 贵,但比其他解决方案便宜。

CE 更容易吸水,从而导致损耗和分层问题。改性氰酸酯环氧树脂具

有更佳的吸水性。最著名的 CE 层压板是 AGC-Nelco N4000-13。另

11

一种基于 CE 的材料是 TUC 的 TU-872LK。

• 聚苯醚 (PPE)

由于其损耗特性,PPE 主要用于高速应用。PPE 的材料比标准

FR-4 更昂贵。松下的 Megtron 6 是最先进入 PPE 领域的,如今已经

有大量基于 PPE 的材料。

• 聚四氟乙烯 (PTFE)

PTFE 层 压 板 具 有 超 低 损 耗、 高 Tg 和 低 吸 水 率。Rogers 和

Taconic 有很多此类材料可供选择,在需要低损耗且可以接受高成本

的军用航空航天应用和天线应用中大量采用。

• 专有树脂

专有树脂体系可能是上述选项的组合。

• 聚酰亚胺

聚酰亚胺是如今第二常用的树脂体系,因为它具有最高的 Tg 值、

非常可靠并且具有挠性。然而,聚酰亚胺存在吸水问题,需要将其烘

烤干燥并用三防漆密封。这使得制造更加困难和昂贵。

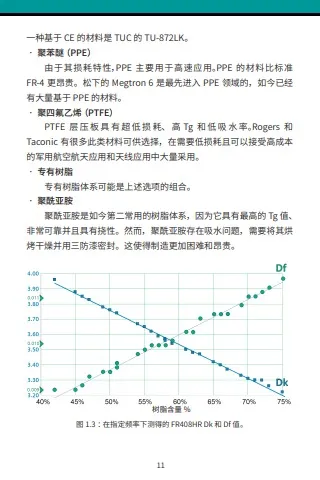

图 1.3 :在指定频率下测得的 FR408HR Dk 和 Df 值。

树脂含量 %

12

玻纤布与树脂的关系

特定材料的介电特性与这两种材料的比例直接相关,它通常被称

为材料树脂含量,通常以百分比为单位,标识树脂所占的百分比。如

图 1.3 所示,同一层压板系统中树脂含量提高会使介电常数(Dk,将

在第 2 章中介绍)降低,同时损耗角正切 (Df) 也会提高。因此,在

计算阻抗(第 5 章)或损耗(第 3 章)时,必须获得准确的树脂含量。

虽然我们在讨论树脂含量百分比,但我要说明的一点是,应该在

半固化片中使用尽可能多的树脂以确保树脂的流动性,填满信号层中

的所有角落和缝隙,不应该由于较高的 Df 值可能会造成损耗而使用

尽可能少的树脂。

IPC 的 PCB 材料标准

IPC 有四个标准是关于刚性多层印制电路板基材的。这些标准包

括 :

• IPC-4101 刚性及多层印制板 基材规范

• IPC-4121 为多层印刷线路板应用选择芯板结构指南

• IPC-4412 印制板用处理“E”玻璃纤维布规范

• IPC-4562 用于印制板应用的金属箔

本书的重点不包括对这些规范的详细探讨,但是在本章的结尾,

我将对 IPC-4101 进行简要介绍。IPC-4101 是包括 66 种材料的“Slash

Sheet”规格表,参考表 1.1 中的第一行,然后可以根据性能规格来

查找对应的材料并进行微调。对于挠性 PCB,请参阅 IPC-4202B。找

到您的应用领域的 Slash Sheet 并熟悉它们非常很有帮助,这样就可

以轻松地将制造商的规格书与规范中列出的化学特性进行比较。

IPC-4101 的 Slash Sheet 中所包含的信息量可能令人望而生畏,

但我认为每个设计 PCB 叠层以及使用或选择材料的人都应该了解这

一标准。这使您能够在层压规格书中遇到 Slash Sheet 时,知道如何

查找。我们将在下一章中详细介绍。

13

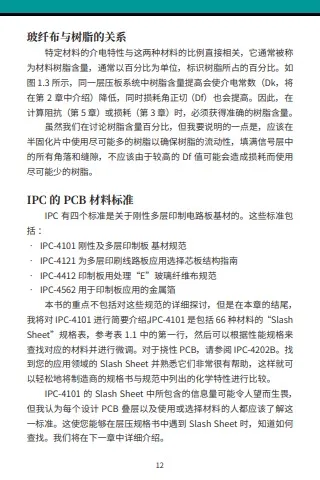

树脂体系 4101/99 4101/101 4101/121 4101/124 4101/126 4101/129

主要成分 环氧树脂 双官能环氧树

脂

双官能环氧树

脂 环氧树脂 环氧树脂 环氧树脂

次要成分 1 多功能环氧树脂 多功能环氧树脂 多功能环氧树脂 多功能环氧树脂 多功能环氧树脂 多功能环氧树脂

次要成分 2 改性或非环氧

(最大 5%)

改性或非环氧

(最大 5%)

改性或非环氧

(最大 5%)

改性或非环氧

(最大 5%)

改性或非环氧

(最大 5%)

改性或非环氧

(最大 5%)

填充剂 包含无机物 包含无机物 不适用 不适用 包含无机物 不适用

热性能

Tg (o

C) 150 110 110 150 170 170

Td (o

C) 325 310 310 325 340 340

Z 轴 CTE

Alpha 1 (max) 60 60 60 60 60 60

Alpha 2 (max) 300 300 300 300 300 300

50 o

C-260 o

C 3.5% 4% 4% 3.5% 3% 3%

T260 (min) 30 30 30 30 30 30

T288 (min) 10 5 5 10 15 15

Frequency

(GHz)

Data Rates

(Gb/s)

Unit Interval

(pSec)

Quarter UI

(pSec)

PCIe 3.0 4 8 125 31

PCI3 4.0 8 16 63 16

PCIe 5.0 16 32 31 8

DF Range Loss Category

≥ 0.021 High loss

0.016 – 0.020 Standard loss

0.011 – 0.015 Mid loss

0.006 – 0.010 Low loss

0.005 – 0.0025 Ultra-low loss

≤ 0.0025 Extremely-low loss

“我建议在完成原理图后立

即进行材料选择。这时, 你

很有可能已经知道了设计的

架构、高速元器件和最快的

边缘速率和比特率是多少,

以及最复杂的 BGA 的外形尺

寸和电路板的形状。”

–Bill Hargin

表 1.1 :IPC-4101 Slash Sheet 的例子。

14

15

第二章

了解材料规格书

当我刚开始进行高速 PCB 设计工作时, 市场上可能有 20 种

左 右 的 层 压 板 材 料, 如 果 是 进 行 高 速 数 字 设 计, 很 可 能 会 使 用

Nelco 的 N4000-13 或 N4000-13 SI 材料。如今有成百上千种选

择, 了解它们的参数的区别非常重要, 通常可以在层压板材料制

造商各个树脂体系的规格书中找到这些参数。如果您想为产品选

择最佳的层压板和电介质材料组合, 就需要知道这些数据的含义

以及如何理解。材料性能的提高必定会使成本提高。本章将会介

绍一些重要的层压板参数, 从而帮助您像在餐厅点菜一样轻松阅

读层压板材料规格书。

一些制造商的规格书的结构可能会更加清晰,但多数情况下,这

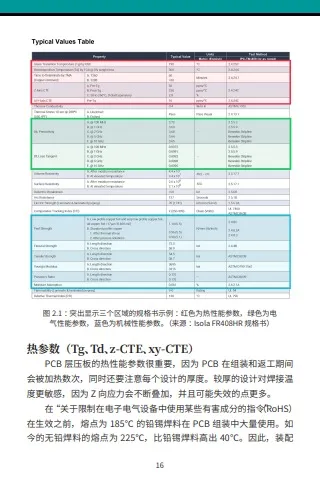

些规格书都会以类似的方式展示数据。如图 2.1 所示,材料规格书中

提供的值通常可分为以下三类 :热性能、电气性能和机械性能参数。

材料是电路板设计的支柱,我们都需要变得更加精明,除了要权衡机

械性能和控制成本之外,更重要的是了解电气性能。

热参数包括玻璃化转变温度 (Tg) 和测试方法、分层时间 (Td)

和热膨胀系数 (CTE) 。

关键电气参数包括介电常数 (Dk) ,也称为相对介电常数 (εr) ,

以及介电损耗 (Df) ,也称为损耗角正切 (tan δ) 。

对于机械参数而言,规格书的详细程度因制造商而异。大多数会

包括剥离强度和吸水率。

16

图 2.1 :突出显示三个区域的规格书示例 :红色为热性能参数,绿色为电

气性能参数,蓝色为机械性能参数。(来源 :Isola FR408HR 规格书)

热参数(Tg、Td、z-CTE、xy-CTE)

PCB 层压板的热性能参数很重要,因为 PCB 在组装和返工期间

会被加热数次,同时还要注意每个设计的厚度。较厚的设计对焊接温

度更敏感,因为 Z 向应力会不断叠加,并且可能失效的点更多。

在“关于限制在电子电气设备中使用某些有害成分的指令” (RoHS)

在生效之前,熔点为 185℃ 的铅锡焊料在 PCB 组装中大量使用。如

今的无铅焊料的熔点为 225℃,比铅锡焊料高出 40℃。因此,装配

17

或返工期间的温度可能会超过 260℃ 数次。

线性热膨胀系数 α 指的是材料随着温度的升高而膨胀的程度。

铜的 CTE 为 16.6 ppm / ℃。导通孔在暴露于较高温度时会以这种速

度膨胀。层压板在 XY 方向上的膨胀相当接近于此数值,但在 Z 方向

上会高不少。

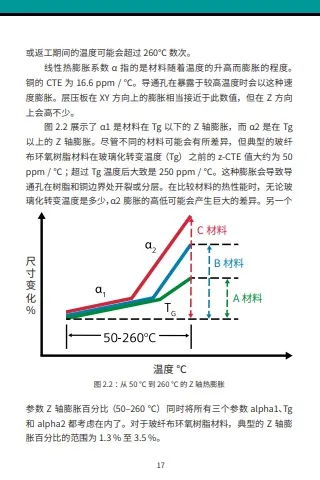

图 2.2 展示了 α1 是材料在 Tg 以下的 Z 轴膨胀,而 α2 是在 Tg

以上的 Z 轴膨胀。尽管不同的材料可能会有所差异,但典型的玻纤

布环氧树脂材料在玻璃化转变温度 (Tg) 之前的 z-CTE 值大约为 50

ppm / ℃ ;超过 Tg 温度后大致是 250 ppm / ℃。这种膨胀会导致导

通孔在树脂和铜边界处开裂或分层。在比较材料的热性能时,无论玻

璃化转变温度是多少,α2 膨胀的高低可能会产生巨大的差异。另一个

参数 Z 轴膨胀百分比 (50–260 ℃) 同时将所有三个参数 alpha1、Tg

和 alpha2 都考虑在内了。对于玻纤布环氧树脂材料,典型的 Z 轴膨

胀百分比的范围为 1.3 % 至 3.5 %。

图 2.2 :从 50 ℃ 到 260 ℃ 的 Z 轴热膨胀

尺

寸

变

化

%

温度 ℃

A 材料

B 材料

C 材料

18

对于较厚的电路板,最好选择玻璃化转变温度较高且 z-CTE 相

对较低的材料。在使用更薄的板设计叠层时,选择中 Tg 材料可以节

省大约 25% 以上的材料成本,这在大批量生产中尤为重要。

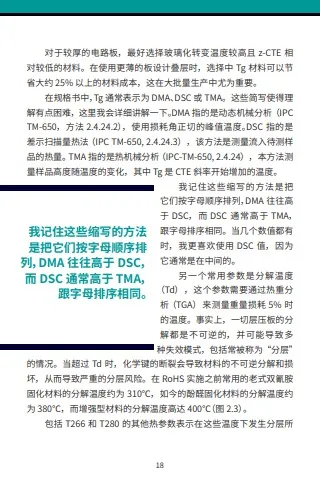

在规格书中,Tg 通常表示为 DMA、DSC 或 TMA。这些简写使得理

解有点困难,这里我会详细讲解一下。 DMA 指的是动态机械分析(IPC

TM-650,方法 2.4.24.2),使用损耗角正切的峰值温度。DSC 指的是

差示扫描量热法 (IPC TM-650, 2.4.24.3) ,该方法是测量流入待测样

品的热量。 TMA 指的是热机械分析 (IPC-TM-650, 2.4.24) ,本方法测

量样品高度随温度的变化,其中 Tg 是 CTE 斜率开始增加的温度。

我记住这些缩写的方法是把

它们按字母顺序排列,DMA 往往高

于 DSC, 而 DSC 通常高于 TMA,

跟字母排序相同。当几个数值都有

时, 我更喜欢使用 DSC 值, 因为

它通常是在中间的。

另一个常用参数是分解温度

(Td) ,这个参数需要通过热重分

析 (TGA) 来测量重量损耗 5% 时

的温度。事实上,一切层压板的分

解都是不可逆的, 并可能导致多

种失效模式,包括常被称为“分层”

的情况。当超过 Td 时,化学键的断裂会导致材料的不可逆分解和损

坏,从而导致严重的分层风险。在 RoHS 实施之前常用的老式双氰胺

固化材料的分解温度约为 310℃,如今的酚醛固化材料的分解温度约

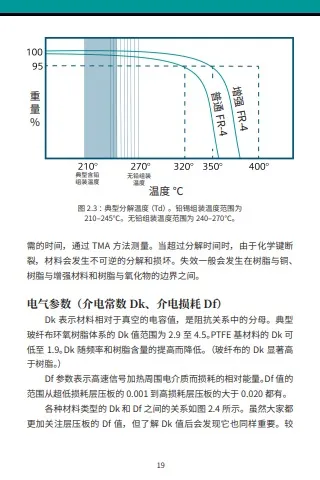

为 380℃,而增强型材料的分解温度高达 400℃(图 2.3)。

包括 T266 和 T280 的其他热参数表示在这些温度下发生分层所

我记住这些缩写的方法

是把它们按字母顺序排

列,DMA 往往高于 DSC,

而 DSC 通常高于 TMA,

跟字母排序相同。

19

图 2.3 :典型分解温度 (Td) 。铅锡组装温度范围为

210–245℃。无铅组装温度范围为 240–270℃。

需的时间,通过 TMA 方法测量。当超过分解时间时,由于化学键断

裂,材料会发生不可逆的分解和损坏。失效一般会发生在树脂与铜、

树脂与增强材料和树脂与氧化物的边界之间。

电气参数(介电常数 Dk、介电损耗 Df)

Dk 表示材料相对于真空的电容值,是阻抗关系中的分母。典型

玻纤布环氧树脂体系的 Dk 值范围为 2.9 至 4.5。PTFE 基材料的 Dk 可

低至 1.9。Dk 随频率和树脂含量的提高而降低。(玻纤布的 Dk 显著高

于树脂。)

Df 参数表示高速信号加热周围电介质而损耗的相对能量。Df 值的

范围从超低损耗层压板的 0.001 到高损耗层压板的大于 0.020 都有。

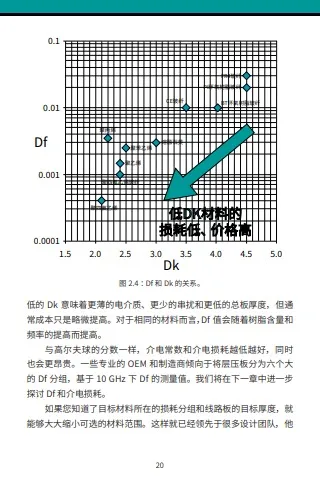

各种材料类型的 Dk 和 Df 之间的关系如图 2.4 所示。虽然大家都

更加关注层压板的 Df 值,但了解 Dk 值后会发现它也同样重要。较

温度 ℃

重

量

%

普通 FR-4

增强 FR-4

典型含铅

组装温度

无铅组装

温度

20

低的 Dk 意味着更薄的电介质、更少的串扰和更低的总板厚度,但通

常成本只是略微提高。对于相同的材料而言,Df 值会随着树脂含量和

频率的提高而提高。

与高尔夫球的分数一样,介电常数和介电损耗越低越好,同时

也会更昂贵。一些专业的 OEM 和制造商倾向于将层压板分为六个大

的 Df 分组,基于 10 GHz 下 Df 的测量值。我们将在下一章中进一步

探讨 Df 和介电损耗。

如果您知道了目标材料所在的损耗分组和线路板的目标厚度,就

能够大大缩小可选的材料范围。这样就已经领先于很多设计团队,他

图 2.4 :Df 和 Dk 的关系。

�.� �.� �.� �.� �.� �.� �.� �.�

Dk

Df

�.�

�.��

�.���

�.����

低DK材料的

损耗低、 价格高

FR�玻纤

PI环氧树脂玻纤

CE玻纤 BT环氧树脂玻纤

聚丙烯

聚苯乙烯

熔融石英

聚乙烯

聚四氟乙烯玻纤

聚四氟乙烯

21

们只会把设计扔给板厂,让板厂来提出建议。

机械参数

材料规格书中所包含的机械参数多少因制造商而异。有些制造商

提供的机械参数包括剥离强度、弯曲强度、吸湿性、导热性、杨氏模

量和泊松比。决定哪些值对您的设计很重要的因素将取决于场景。

弯曲强度、杨氏模量和剥离强度是材料在各种测试条件下的强度

测量值。大多数材料规格书至少会包括剥离强度和吸水率。

由于多种因素的影响,包括周围环境或工艺温度的变化、制造过

程中材料的暴露时间、湿法 PCB 制造工艺的影响、储存条件、层厚

度、包装、树脂类型和树脂含量等,层压板会吸收水分。

无论水分是怎么来的,在层压之后,铜层都会起到防水层的作

用,这可能会导致在焊接制程中内部蒸汽压力积聚的地方出现分层。

此外,由于水分子是对称的,它们的存在会增加材料的实际 Df 值以

及相关的介电损耗。玻纤布环氧树脂体系的吸水率通常在 0.05% 到

0.30% 之间,更好的材料会低于 0.20%。聚酰亚胺体系的吸水率约

为 0.35%,因此,使用聚酰亚胺的电路板通常需要烘烤并用三防漆

密封。

剥离强度表征的是材料中的树脂对铜的粘附力。测量值以磅力每

英寸 (lbf/in) 或牛顿每米 (N/m) 为单位,在材料暴露于高温和特定

化学品后进行测试。可能会列出多个值,包含不同的测试条件和不同

的铜厚的测试结果。数值范围为 3–10 磅 / 英寸,剥离强度通常约为

6–8 磅 / 英寸。

在第 3 章中,我们将深入探讨介电材料的损耗因子及其对损耗的

影响。

23

第三章

降低损耗

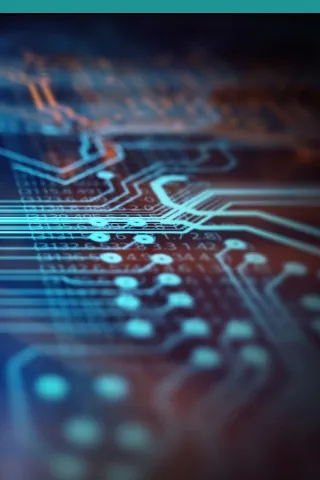

在本章中,我们将讨论与叠层相关的信号损耗,以及如何为特定

应用选择最佳层压板材料,并同时避免欠设计或过度设计的过程。

由于如今的高速 PCB 应用中更快的上升时间,传输线的损耗效

应会极大地影响信号质量。如图 3.1 所示,在较高频率下,损耗和上

升时间衰减跟走线互连长度有直接关系。

需要考虑两个重要的导致信号能量损耗的机制 :介电损耗以及由

“趋肤效应”和铜箔粗糙度引起的导体损耗。

图 3.1 :10-40 英寸线路上无损互连(橙色)和有损

电介质的上升时间衰减和衰减(损耗)。

时间

Voltage

�� - in. Lossy

�� - in. Lossy

�� - in. Lossy

Lossless

衰减

上升时间衰减

时间

电

压

无损

20 英寸损耗

40 英寸损耗

10 英寸损耗

24

介电损耗

介电损耗会随着频率

和材料的损耗角正切或介电

损耗因数 (Df) 的提高而提

高。标准 FR-4 材料属于高

损 耗 类 别, 损 耗 角 正 切 为

0.02–0.03。 损 耗 较 低 的 材

料价格相应更高,目前一些超低损耗和极低损耗材料的高端层压板的

Df 值低于 0.0025,如表 3.1 所示。

“趋肤效应”引起的导体损耗

在 DC 和数 MHz 的频率时,走线中的电流会流过导体的整个横

截面积。在较高频率下,电流会沿着导体的表面传输,而不是均匀地

流过整个横截面。其结果是互连线路的有效横截面积减小,信号的串

联电阻和返回导体路径会随着频率均方根的增加而增加。

铜箔粗糙度引起的导体损耗

由于对高频损耗的影响,信号层上的铜箔表面形貌(粗糙度)变

得越来越重要。例如,在 5 GHz (约 10 Gb/s) 下,10 英寸的线路从极

粗糙(Rz = 8.5 µm)到极光滑(Rz = 1 µm)的损耗变化高达 2 dB。

频率越高导致的损耗差距越大,光滑且更昂贵的铜已经成为了减少互

连损耗的关键武器。

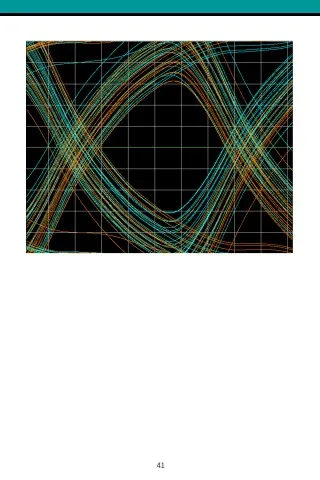

眼图和眼图模板

示波器眼图可以显示互连的位转换是否可以被接受。合格 / 不合

格的标准通常由眼图模板确定,例如图 3.2 中的蓝色六边形。符合不

同 SERDES 规范的眼图模板定义了不应出现位转换的最小和最大禁

表 3.1 :Df 范围与损耗组。

df 范围 损耗分组

高损耗

标准损耗

中等损耗

低损耗

超低损耗

极低损耗

25

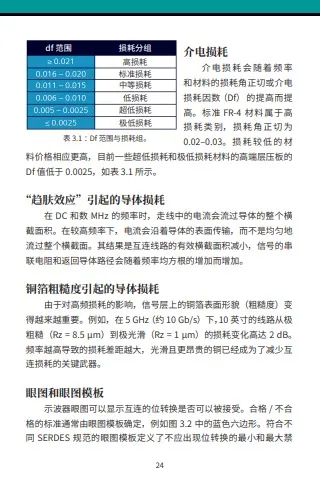

图 3.2 :西门子 HyperLynx 软件中的 Intel PCI Express 5.0 眼图模板。

止区域,以便接收器正确理解发送端的意图。

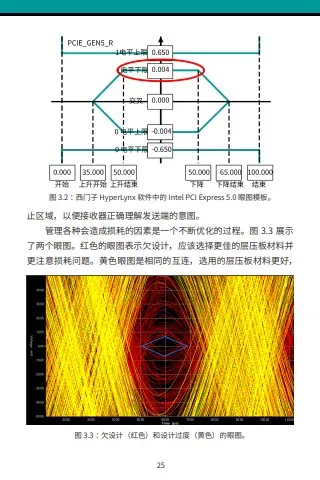

管理各种会造成损耗的因素是一个不断优化的过程。图 3.3 展示

了两个眼图。红色的眼图表示欠设计,应该选择更佳的层压板材料并

更注意损耗问题。黄色眼图是相同的互连,选用的层压板材料更好,

图 3.3 :欠设计(红色)和设计过度(黄色)的眼图。

26

但裕量有一些过大。对于更昂贵的系统而言,可以使用发送端预加重

或接收端均衡等控制损耗的技术。它们得成本和功耗都更高。在控制

互连损耗的所有方法中,对层压板材料进行优化是成本最低的。

我推荐的损耗和材料规划方法

在我讲授叠层设计的研讨会上,有时有人会问我 :“最好的低损

耗层压板材料是哪种? ” 我会推荐我的规划方法来回应这个问题,接

下来将会简要介绍这种方法。

这个问题的答案取决于产品的互连标准、衰减预算、目标互连

长度、电路板的制造商以及预算。许多参数会影响损耗 :频率、铜厚、

树脂体系、玻纤布类型、电介质厚度、走线宽度、铜箔粗糙度和板厂

制程。

接下来,我将通过一个例子来阐明这种方法。我所开发的软件

Z-planner Enterprise 可以用于缩小选择范围。Z-planner Enterprise

是一个全面的、基于场求解器的叠层规划工具,包含在西门子 EDA

解决方案中。

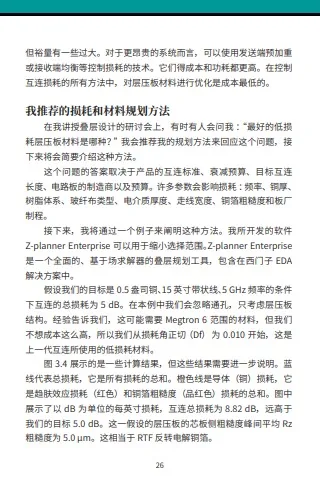

假设我们的目标是 0.5 盎司铜、15 英寸带状线、5 GHz 频率的条件

下互连的总损耗为 5 dB。在本例中我们会忽略通孔,只考虑层压板

结构。经验告诉我们,这可能需要 Megtron 6 范围的材料,但我们

不想成本这么高,所以我们从损耗角正切 (Df) 为 0.010 开始,这是

上一代互连所使用的低损耗材料。

图 3.4 展示的是一些计算结果,但这些结果需要进一步说明。蓝

线代表总损耗,它是所有损耗的总和。橙色线是导体(铜)损耗,它

是趋肤效应损耗(红色)和铜箔粗糙度(品红色)损耗的总和。图中

展示了以 dB 为单位的每英寸损耗,互连总损耗为 8.82 dB,远高于

我们的目标 5.0 dB。这一假设的层压板的芯板侧粗糙度峰间平均 Rz

粗糙度为 5.0 µm。这相当于 RTF 反转电解铜箔。

27

图 3.4:初始带状线配置 Df=0.010,总损耗为 8.82 dB。

(图片来自 Z-planner Enterprise 软件)

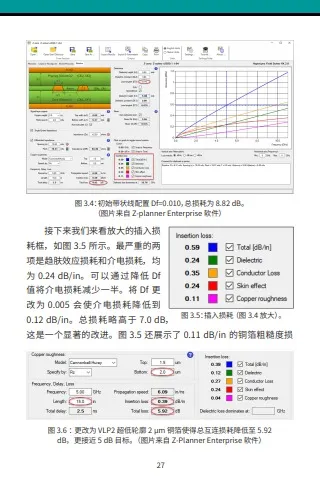

接下来我们来看放大的插入损

耗框,如图 3.5 所示。最严重的两

项是趋肤效应损耗和介电损耗,均

为 0.24 dB/in。可 以 通 过 降 低 Df

值将介电损耗减少一半。将 Df 更

改为 0.005 会使介电损耗降低到

0.12 dB/in。总损耗略高于 7.0 dB,

这是一个显著的改进。图 3.5 还展示了 0.11 dB/in 的铜箔粗糙度损

图 3.5:插入损耗 (图 3.4 放大)。

图 3.6 :更改为 VLP2 超低轮廓 2 µm 铜箔使得总互连损耗降低至 5.92

dB,更接近 5 dB 目标。(图片来自 Z-Planner Enterprise 软件)

28

耗,它跟新的介电损耗所带来的改善很接近。

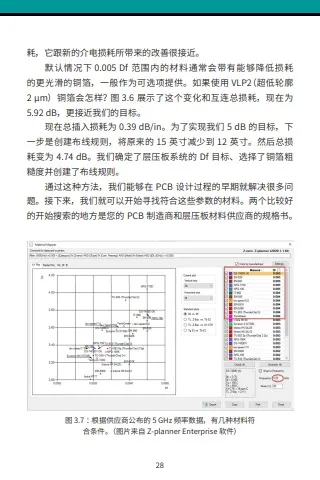

默认情况下 0.005 Df 范围内的材料通常会带有能够降低损耗

的更光滑的铜箔,一般作为可选项提供。如果使用 VLP2(超低轮廓

2 µm)铜箔会怎样? 图 3.6 展示了这个变化和互连总损耗,现在为

5.92 dB,更接近我们的目标。

现在总插入损耗为 0.39 dB/in。为了实现我们 5 dB 的目标,下

一步是创建布线规则,将原来的 15 英寸减少到 12 英寸。然后总损

耗变为 4.74 dB。我们确定了层压板系统的 Df 目标、选择了铜箔粗

糙度并创建了布线规则。

通过这种方法,我们能够在 PCB 设计过程的早期就解决很多问

题。接下来,我们就可以开始寻找符合这些参数的材料。两个比较好

的开始搜索的地方是您的 PCB 制造商和层压板材料供应商的规格书。

图 3.7 :根据供应商公布的 5 GHz 频率数据,有几种材料符

合条件。(图片来自 Z-planner Enterprise 软件)

29

图 3.7 展示了几种可能符合条件的材料,这些材料基于供应商公布的

5 GHz 频率的 Df 数值。

如果您可以像这样在设计过程的早期就确定采用哪种材料,就可

以避免样机制造时出现的各种意外或过度设计,为不必要的过剩性能

支付更高的费用。尽早做出这些选择还意味着您可以避免因为层压板

材料交期过长导致样机制造或生产周期延迟。

与生活中很多其他事情一样,提前做好计划可以让您有更多的选

项和更少的意外。您可以把计划使用的实际层压系统的 Dk 和 Df 数

据输入昂贵的信号完整性软件。此外,计划还可以使新产品导入 (NPI)

更准时,同时减轻 PCB 供应商的一些压力。如果能够在设计过程的

早期就确定 PCB 叠层最适合的材料,那么每个人都将是赢家。

31

第四章

材料鉴定与选择

在上一章中,我介绍了如何根据损耗要求进行材料选择。在本章

中,我们将进一步探讨如何鉴定材料以及为特定的最终应用做出选择。

材料鉴定

经验丰富的制造商会告诉您他们的层压板材料适用的单板厚

度范围。在第一章中,我们了解了如何按照电路板厚度来选择玻璃

化转变温度。但并非所有 170℃ 材料都适用于 93 至 130 mil 的电

路板厚度。虽然高 Tg 材料不易分层,但还应考虑 z-CTE 值,包括

50–260℃ 的 Z 轴膨胀百分比。在第二章中详细描述的这些参数应

该用于首轮对比,而除了规格书中的参数外,在用于高层数设计时,

每种材料的相对性能仍然可能存在差异。

随着层数和电路板厚度的增加,热应力会累积,导通孔孔壁镀

层所承受的应力越大,并且会提高在树脂和铜边界处分层的风险。

这不是一个绝对的规则,但 16 层似乎是一个比较明显的分界线,

一些材料在 16 层以内表现良好,但超出 16 层就会出现失效。超过

16 层后,在进行系统的材料可靠性测试之前无法获知材料的性能。

可以使用能够代表该设计的标准测试样品的可靠性测试结果来

创建可选材料清单,PCB 制造商也有可能会分享类似的测试结果。

必须仔细评估电路板的厚度、层数和 BGA 间距,以确保测试结果

能够代表您的电路板设计。

32

选择层压材料系统

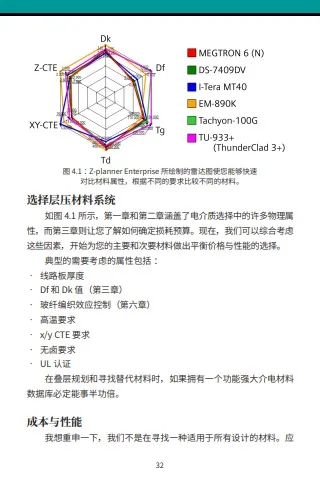

如图 4.1 所示,第一章和第二章涵盖了电介质选择中的许多物理属

性,而第三章则让您了解如何确定损耗预算。现在,我们可以综合考虑

这些因素,开始为您的主要和次要材料做出平衡价格与性能的选择。

典型的需要考虑的属性包括 :

• 线路板厚度

• Df 和 Dk 值(第三章)

• 玻纤编织效应控制(第六章)

• 高温要求

• x/y CTE 要求

• 无卤要求

• UL 认证

在叠层规划和寻找替代材料时,如果拥有一个功能强大介电材料

数据库必定能事半功倍。

成本与性能

我想重申一下,我们不是在寻找一种适用于所有设计的材料。应

图 4.1 :Z-planner Enterprise 所绘制的雷达图使您能够快速

对比材料属性,根据不同的要求比较不同的材料。

33

该为您的设计寻找的是价格合理、可替换并且可靠的材料。即使成本

差异只是几美分,但在大批量生产中也会累计起来。

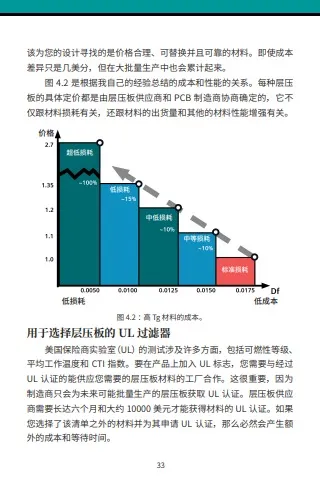

图 4.2 是根据我自己的经验总结的成本和性能的关系。每种层压

板的具体定价都是由层压板供应商和 PCB 制造商协商确定的,它不

仅跟材料损耗有关,还跟材料的出货量和其他的材料性能增强有关。

用于选择层压板的 UL 过滤器

美国保险商实验室 (UL) 的测试涉及许多方面,包括可燃性等级、

平均工作温度和 CTI 指数。要在产品上加入 UL 标志,您需要与经过

UL 认证的能供应您需要的层压板材料的工厂合作。这很重要,因为

制造商只会为未来可能批量生产的层压板获取 UL 认证。层压板供应

商需要长达六个月和大约 10000 美元才能获得材料的 UL 认证。如果

您选择了该清单之外的材料并为其申请 UL 认证,那么必然会产生额

外的成本和等待时间。

图 4.2 :高 Tg 材料的成本。

低损耗 低成本

价格

标准损耗

中等损耗

中低损耗

低损耗

超低损耗

34

不幸的是,没有任何一个在线数据库可以显示哪些制造商拥有哪

些经过 UL 认证的材料。必须查看他们的 UL 文件或询问。通常,他

们将此作为销售的机会。当层压板供应商开发出一种新材料时,他们

必须自己对该材料进行 UL 认证。然后当板厂得到这些新层压板时,

板厂还需要再进行一次 UL 认证。

如第二章所述,较厚的电路板需要较高的 Tg 值。原因是层压板

(和叠层)的 z 轴热膨胀在高于玻璃化转变温度时急剧上升。根据

Tg 选择材料的一般经验法则如图 4.3 所示,但还应考虑其他热特性,

包括从 50℃ 到 260℃ 的 z 轴膨胀和分解温度 (Td) 。此外,虽然经

验法则提供了一般性指导,但它们不能代替正式的材料鉴定,此话题

超出了本书的讨论范围,就不展开了。

定价

购买层压板不像在亚马逊上购物或在 Digikey 上购买电阻元件。

层压板供应商不会公开化学配方和价格。他们会根据数量、材料成本

以及特定材料的市场影响力与 PCB 板厂协商价格。

图 4.3 :建议的板厚度与 Tg 关系。

如 28 层

如 20 层

如 12 层

高

中

低

PCB 厚度 > 130 mil

• 使用的材料 Tg 应高于 220℃

PCB 厚度 70~130 mil

• 使用的材料 Tg 应高于 170℃

PCB 厚度 60~70 mil

• 使用的材料 Tg 应高于 155℃

PCB 厚度 < 60 mil

• 使用的材料 Tg 应高于 135℃

35

通常,层压板供应商不会为产品给出固定价格。他们的销售人员

会根据数量、位置,有时还会根据原材料成本的波动与 PCB 制造商

进行谈判。层压板成本通常会影响裸电路板的价格。

北美的层压板制造商倾向于给出包含了足够利润的标准化定价来

应对原材料价格波动。亚洲的许多层压板制造商的利润率较低,这可

能导致价格波动,具体价格取决于时间、铜箔价格、树脂和玻纤布价

格以及数量。

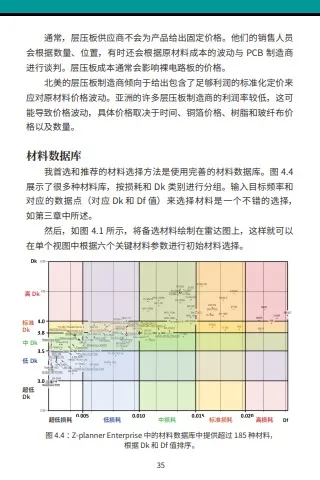

材料数据库

我首选和推荐的材料选择方法是使用完善的材料数据库。图 4.4

展示了很多种材料库,按损耗和 Dk 类别进行分组。输入目标频率和

对应的数据点(对应 Dk 和 Df 值)来选择材料是一个不错的选择,

如第三章中所述。

然后,如图 4.1 所示,将备选材料绘制在雷达图上,这样就可以

在单个视图中根据六个关键材料参数进行初始材料选择。

图 4.4 :Z-planner Enterprise 中的材料数据库中提供超过 185 种材料,

根据 Dk 和 Df 值排序。

高 Dk

标准

Dk

中 Dk

低 Dk

超低

Dk

超低损耗 低损耗 中损耗 标准损耗 高损耗

36

37

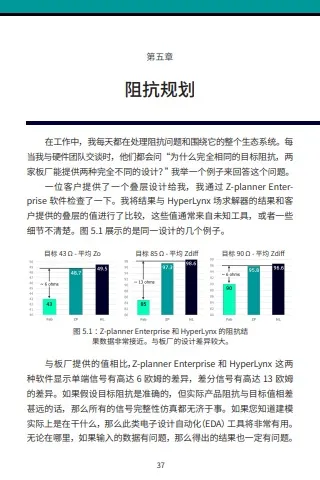

在工作中,我每天都在处理阻抗问题和围绕它的整个生态系统。每

当我与硬件团队交谈时,他们都会问“为什么完全相同的目标阻抗,两

家板厂能提供两种完全不同的设计? ” 我举一个例子来回答这个问题。

一位客户提供了一个叠层设计给我, 我通过 Z-planner Enterprise 软件检查了一下。我将结果与 HyperLynx 场求解器的结果和客

户提供的叠层的值进行了比较,这些值通常来自未知工具,或者一些

细节不清楚。图 5.1 展示的是同一设计的几个例子。

与板厂提供的值相比,Z-planner Enterprise 和 HyperLynx 这两

种软件显示单端信号有高达 6 欧姆的差异,差分信号有高达 13 欧姆

的差异。如果假设目标阻抗是准确的,但实际产品阻抗与目标值相差

甚远的话,那么所有的信号完整性仿真都无济于事。如果您知道建模

实际上是在干什么,那么此类电子设计自动化 (EDA) 工具将非常有用。

无论在哪里,如果输入的数据有问题,那么得出的结果也一定有问题。

第五章

阻抗规划

图 5.1 :Z-planner Enterprise 和 HyperLynx 的阻抗结

果数据非常接近。与板厂的设计差异较大。

目标 43 Ω - 平均 Zo 目标 85 Ω - 平均 Zdiff 目标 90 Ω - 平均 Zdiff

38

因素 类型 排名 描述 影响 占比

介电厚度

材料

1 芯板 厚度一致性

2 半固化片 51.0% 树脂含量;树脂流

动性和铜箔%

制程 3 层压 PCB 厚度

介电常数 材料 4

芯板 树脂含量;频率;

测量方法 22.0%

半固化片

走线宽度 制程 5

曝光 曝光侧蚀

18.5%

蚀刻 蚀刻系数

铜箔厚度 制程 6 电镀和刷磨 分布;

电流密度 5.5%

阻焊层厚度

材料

7

油墨粘度

走线厚度;线距 3.0%

制程 打印

100.0%

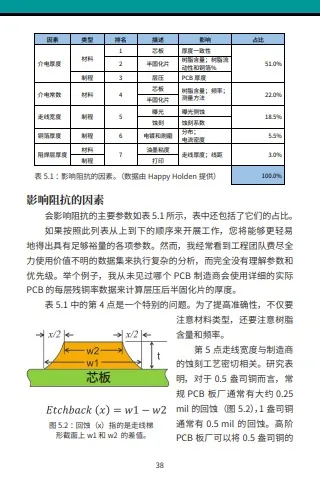

影响阻抗的因素

会影响阻抗的主要参数如表 5.1 所示,表中还包括了它们的占比。

如果按照此列表从上到下的顺序来开展工作,您将能够更轻易

地得出具有足够裕量的各项参数。然而,我经常看到工程团队费尽全

力使用价值不明的数据集来执行复杂的分析,而完全没有理解参数和

优先级。举个例子,我从未见过哪个 PCB 制造商会使用详细的实际

PCB 的每层残铜率数据来计算层压后半固化片的厚度。

表 5.1 中的第 4 点是一个特别的问题。为了提高准确性,不仅要

注意材料类型,还要注意树脂

含量和频率。

第 5 点走线宽度与制造商

的蚀刻工艺密切相关。研究表

明,对于 0.5 盎司铜而言,常

规 PCB 板厂通常有大约 0.25

mil 的回蚀(图 5.2),1 盎司铜

通常有 0.5 mil 的回蚀。高阶

PCB 板厂可以将 0.5 盎司铜的

表 5.1 :影响阻抗的因素。(数据由 Happy Holden 提供)

图 5.2 :回蚀(x)指的是走线梯

形截面上 w1 和 w2 的差值。

芯板

39

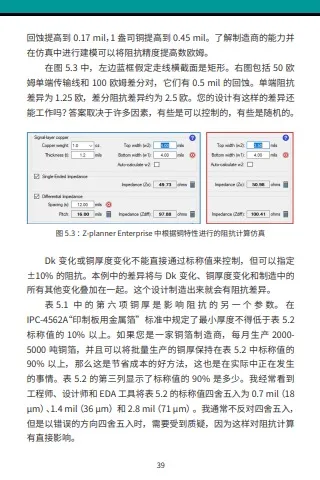

图 5.3 :Z-planner Enterprise 中根据铜特性进行的阻抗计算仿真

回蚀提高到 0.17 mil,1 盎司铜提高到 0.45 mil。了解制造商的能力并

在仿真中进行建模可以将阻抗精度提高数欧姆。

在图 5.3 中,左边蓝框假定走线横截面是矩形。右图包括 50 欧

姆单端传输线和 100 欧姆差分对,它们有 0.5 mil 的回蚀。单端阻抗

差异为 1.25 欧,差分阻抗差异约为 2.5 欧。您的设计有这样的差异还

能工作吗? 答案取决于许多因素,有些是可以控制的,有些是随机的。

Dk 变化或铜厚度变化不能直接通过标称值来控制,但可以指定

±10% 的阻抗。本例中的差异将与 Dk 变化、铜厚度变化和制造中的

所有其他变化叠加在一起。这个设计制造出来就会有阻抗差异。

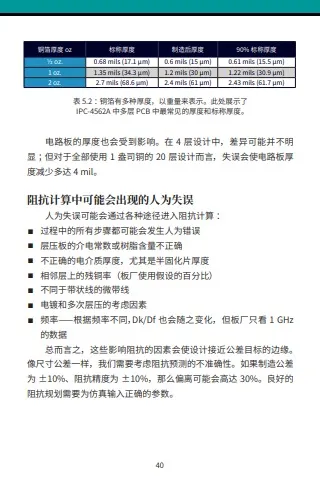

表 5.1 中 的 第 六 项 铜 厚 是 影 响 阻 抗 的 另 一 个 参 数。 在

IPC-4562A“印制板用金属箔”标准中规定了最小厚度不得低于表 5.2

标称值的 10% 以上。如果您是一家铜箔制造商, 每月生产 2000-

5000 吨铜箔,并且可以将批量生产的铜厚保持在表 5.2 中标称值的

90% 以上,那么这是节省成本的好方法,这也是在实际中正在发生

的事情。表 5.2 的第三列显示了标称值的 90% 是多少。我经常看到

工程师、设计师和 EDA 工具将表 5.2 的标称值四舍五入为 0.7 mil (18

μm) 、1.4 mil (36 μm) 和 2.8 mil (71 μm) 。我通常不反对四舍五入,

但是以错误的方向四舍五入时,需要受到质疑,因为这样对阻抗计算

有直接影响。

40

电路板的厚度也会受到影响。在 4 层设计中,差异可能并不明

显 ;但对于全部使用 1 盎司铜的 20 层设计而言,失误会使电路板厚

度减少多达 4 mil。

阻抗计算中可能会出现的人为失误

人为失误可能会通过各种途径进入阻抗计算 :

∎ 过程中的所有步骤都可能会发生人为错误

∎ 层压板的介电常数或树脂含量不正确

∎ 不正确的电介质厚度,尤其是半固化片厚度

∎ 相邻层上的残铜率(板厂使用假设的百分比)

∎ 不同于带状线的微带线

∎ 电镀和多次层压的考虑因素

∎ 频率——根据频率不同,Dk/Df 也会随之变化,但板厂只看 1 GHz

的数据

总而言之,这些影响阻抗的因素会使设计接近公差目标的边缘。

像尺寸公差一样,我们需要考虑阻抗预测的不准确性。如果制造公差

为 ±10%、阻抗精度为 ±10%,那么偏离可能会高达 30%。良好的

阻抗规划需要为仿真输入正确的参数。

表 5.2 :铜箔有多种厚度,以重量来表示。此处展示了

IPC-4562A 中多层 PCB 中最常见的厚度和标称厚度。

Factors Type Rank Description Infl uence Contribution

Dielectric Thickness Material

1 Core Thickness uniformity

2 Prepreg 51% Resin content; resin fl ow

and % copper

Process 3 Lamination Board thickness

Dielectric Constant Material 4

Core Resin content;

frequency;

measurement method

22% Prepreg

Trace Width Process 5 Exposure Exposure undercut 18.5% Etching Etch factor

Copper Thickness Process 6 Plating &

scrubbing

Distribution; current

density 5.5%

Solder Mask Thickness Material 7 Ink viscosity Trace thickness;

gaps/spacing 3% Process Printing

100%

铜箔厚度 oz 标称厚度 制造后厚度 90% 标称厚度

½ oz. 0.68 mils (17.1 μm) 0.6 mils (15 μm) 0.61 mils (15.5 μm)

1 oz. 1.35 mils (34.3 μm) 1.2 mils (30 μm) 1.22 mils (30.9 μm)

2 oz. 2.7 mils (68.6 μm) 2.4 mils (61 μm) 2.43 mils (61.7 μm)

41

该页无缩略图

该页无缩略图